Research and Innovation

Our expertise in the research domain can help you accelerate your research projects in every field, from IOT to 5G, from Smart Grid to Oil and Gas.

Now more than ever, there is a need for reliable and timely research in every domain, be it transportation, wireless communications, medicine, energy or climate change, among others. Research, development and innovation are key to industrial development in the world of Industry 4.0, where technology transfer and collaboration between research institutions and industry is key.

Across each of these application areas, researchers need to easily acquire measurements, scale to complex multidisciplinary systems, and rapidly prototype a scalable solution. We work with the top research players to provide the technology and support to prototype systems, publish findings and secure funding.

Some of our Research Solutions

More resources

Research Webinars

Access the recordings of this three-part webinar series on self-driving vehicles, manipulator robotics and earthquake engineering.

Are you on a tight budget?

We know you want to advance your research project but you probably struggle with:

- balancing costs

- tight schedules

- reliability metrics.

We work with the top research solutions providers to help you overcome all those obstacles. Here are some examples of solutions to help you with your Research Projects:

• RIOsys: RIOsys is an open platform that helps the engineers and researchers to easily and cost-effectively design their solutions in the field of energy. Due to its openness, available software framework and affordable cost RIOsys is the best fit for both research & prototyping and for mass deployment.

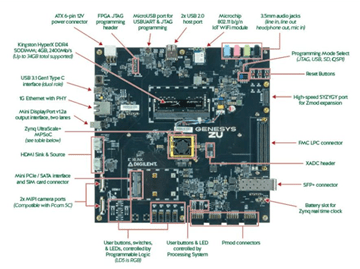

• Genesys ZU – Computing & acceleration platform: demonstrate key capabilities and algorithms running on hardware early in the development cycle to reduce risk before the final application can be deployed to the field.

• Eclypse Z7 Signal Processing Ecosystem allows you to get up and running in hours or days, instead of weeks or months.

Genesys ZU – Computing & acceleration platform

Developing embedded systems is challenging, throughout the development cycle capabilities must be demonstrated and risks retired before the final application can be deployed to the field. One of the main way’s risks can be retired and the technology readiness level increased is to demonstrate key capabilities and algorithms running on hardware early in the development cycle, this is where development boards such as the Genesys ZU comes into its own. The Genesys ZU with its wide range of interfacing capabilities enables rapid prototyping and risk reduction on target hardware.

The Digilent Genesys ZU is a standalone Zynq UltraScale+ EG MPSoC development board, designed to provide an ideal entry point by combining cost-effectiveness with powerful multimedia and network connectivity interfaces. The Genesys ZU supports multiple camera inputs, 4K video, 1G/10G Ethernet with high-memory bandwidth in a heavily Linux-based platform, serving as an advanced reVISION system. Two different specialized ports, including Pmod and high-speed SYZYGY – compliant expansion module ports for our new Zmods, enable flexible expansion and easy access to a wide ecosystem of add-on modules, perfect for silicon evaluation and rapid prototyping.

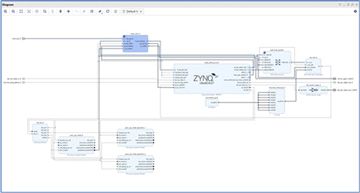

In order to create the platform, you can make use of Digilent software support including MIPI CSI-2/Pcam PL softcore, DisplayPort controller and out of the box Petalinux to build the hardware design. A simple application software is created so that HD video signals stream through Genesys ZU-3EG and are output at the on board.

See the technology in action: Accelerate developing embedded systems using Xilinx Vitis and Genesys ZU

The latest Xilinx Vitis integrated software platform enables the development of embedded software and accelerated applications running on heterogeneous Xilinx platforms, including FPGAs and SoCs, enabling edge computing, cloud computing, and hybrid computing-based applications. It provides an integrated programming model that accelerates C/C++, OpenCL or Python language development using accelerated libraries or RTL-based accelerators and low-level runtimes APIs for more control over implementation. This allows engineers and developers to choose the level of abstraction they want and run programmable logic without using a hardware description language (HDL).

For more info, visit the Digilent Project page

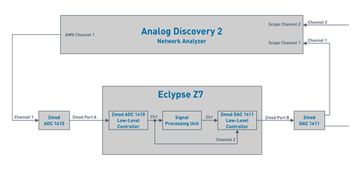

Eclypse Z7 Signal Processing Ecosystem

The Eclypse Z7 ecosystem includes Eclypse Z7 development platform, the Zmod ADC 1410 and Zmod DAC 1411. Both Zmods are 100 MSPS and 14-bit data converters. The Eclypse Z7 development platform features a Zynq 7020 FPGA SoC from Xilinx and two high-speed connectors using Opal Kelly’s new SYZYGY standard, which pairs with Digilent’s new Zmod family to allow for high performance I/O. Plug in your application specific Zmods and get up and running in hours or days, instead of weeks or months.

The Zmod ADC 1410 is equipped with Analog Devices AD9648, the dual channel, high speed, low power, 14-bit, 105MS/s Analog to Digital Converter (ADC). Driven by the SYZYGY carrier, the Zmod ADC can acquire two simultaneous signals (1MΩ, ±25V, single-ended, 14-bit, 100MS/s, 70MHz+ bandwidth). Analog inputs can be connected to a circuit using SMA cables.

The Zmod DAC 1411 is equipped with Analog Devices AD9717, the dual channel, high speed, low power, 14-bit, 125MS/s Digital to Analog Converter (DAC). Driven by the SYZYGY carrier, the Zmod DAC can generate two simultaneous signals (50Ω, ±5V, single-ended, 14-bit, 100MS/s, 40MHz+ bandwidth). The analog outputs can be connected to a circuit using SMA cables.

See the technology in action: FPGA-based Implementation of Signal Processing System

Signal processing applications require high computing performance and power efficiency. The Eclypse platform (Eclypse Z7 + Zmod ADC + Zmod DAC) can provide the solution. It comes with a free example project which shows users the implementation of a signal processing system.

For this specific project the Zmod ADC 1410 will be the Low Level Controller that initializes the Zmod ADC 1410 hardware and synchronizes the incoming data in the user clock domain. A digital low pass filter is used in the project and implemented using Xilinx FIR compiler 7.2 IP Core. In this case the Zmod DAC 1411 initializes the Zmod DAC 1411 hardware and formats the output data according to the AD9717 DAC requirements. The Network Analyzer will be used to generate a sinusoidal signal (perturbation) on the AWG1 channel. The bode plot is obtained considering the loopback signal (Zmod DAC 411 CH2) as reference.

The project details and source files are available at Digilent Resource Center.